北京大学黄如院士团队在“存内计算AI芯片”领域取得重要成果

2022年2月末,有着“集成电路国际奥林匹克盛会”之称的IEEE国际固态电路会议(International Solid-State Circuits Conference, ISSCC)圆满举办。ISSCC是世界学术界和企业界公认的集成电路设计领域最高级别会议。

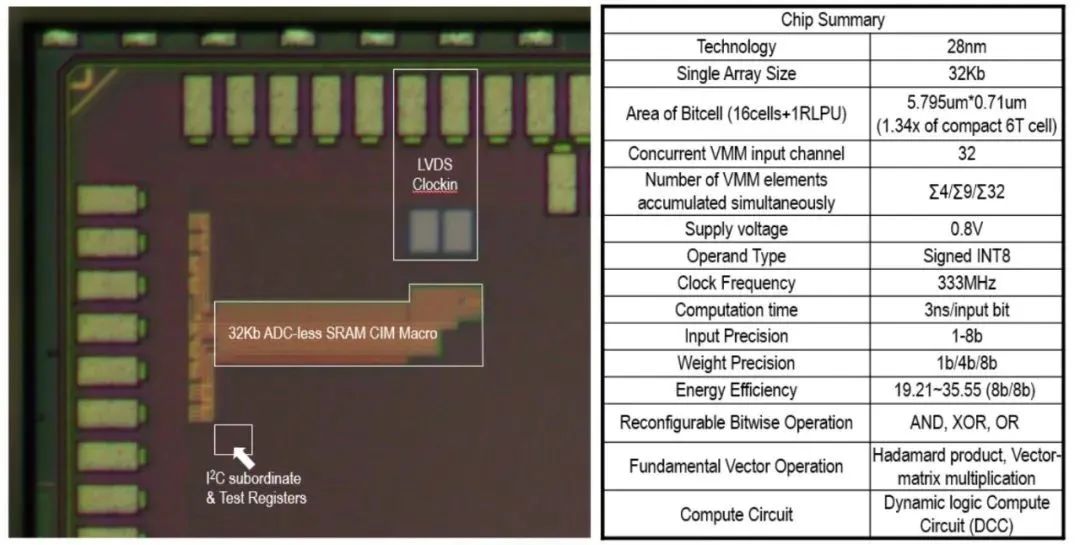

在此次会议上,北京大学集成电路学院与人工智能研究院黄如院士——燕博南助理教授课题组关于存内计算的的学术文章《A 1.041Mb/mm2 27.38TOPS/W Signed-INT8 Dynamic Logic Based ADC-Less SRAM Compute-In-Memory Macro in 28nm with Reconfigurable Bitwise Operation for AI and Embedded Applications》收录于“Session 11 存内计算与SRAM”专题(文章号11.7)。

此工作提出高效的无ADC架构SRAM存内计算加速引擎,基于28nm工艺搭建模块可以达到27.38TOPS/W@INT8的高能效比,同时实现高达1.041Mb/mm2密度,达到国际领先指标并实现技术突破。

该工作合作者有北京苹芯科技有限公司、NeoNexus Group与杜克大学。课题组获得了北京大学人工智能研究院、北京苹芯科技等资助。

下附本工作与课题组的简介:

全数字型存内计算技术路线

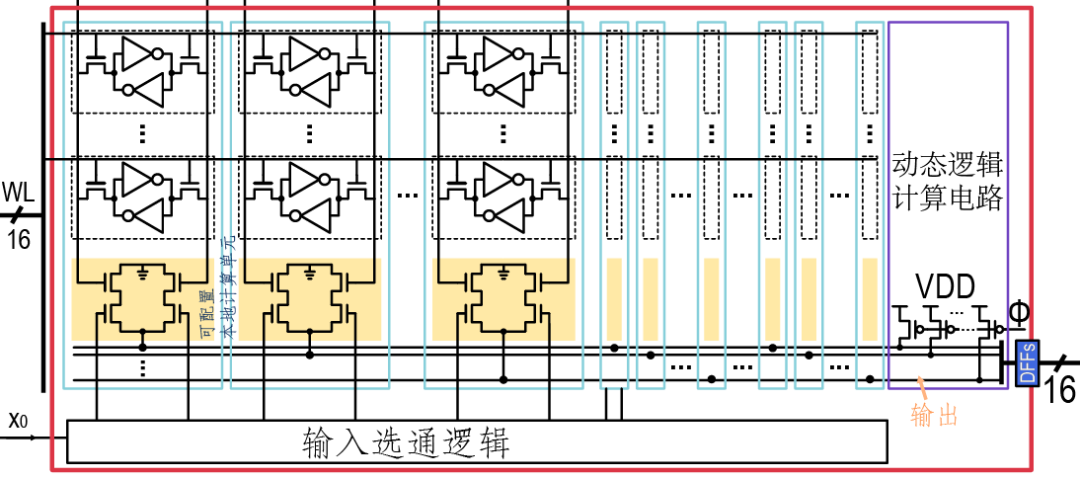

此工作实现了28nm 技术节点的32Kb无 ADC的SRAM存内计算加速单元,由动态逻辑计算电路替代传统模数转换或CMOS静态逻辑,达到高能效比与面效比。同时由分布于存储器阵列内的可重构本地处理单元(Reconfigurable Local Process Units,RLPU)实现bitcell级的数组逻辑运算,并拓展至向量矩阵相关计算(VHP/VMM),在核心指标方面相较于传统架构具备数量级优势,为存内计算技术的实际产业化应用部署奠定坚实基础。

存内计算芯片演示

存内计算芯片主要用于深度学习网络中海量乘加计算的加速。课题组还利用原型芯片进行了常见的神经网络的实际演示,在ISSCC的演示环节受到广泛好评。演示视频链接:

https://www.bilibili.com/video/BV15b4y1H7gP

黄如院士-燕博南助理教授课题组简介

燕博南助理教授, 2020年于美国杜克大学获得电子与计算机博士学位,后入职北京大学人工智能研究院从事人工智能与芯片交叉方向研究。主要研究方向包括:

· 新兴存储器集成电路设计

· 存算一体化电路与系统

· 人工智能计算机微架构

课题组常年招收志在探索未知、勇于创新的本科生与研究生,合作与招生相关问题请直接联系Email:bonanyan@pku.edu.cn。

ISSCC会议介绍

ISSCC(IEEE International Solid-State Circuits Conference,国际固态电路会议),是世界学术界和企业界公认的集成电路设计领域最高级别会议,被认为是集成电路设计领域的“奥林匹克大会”。世界上第一个TTL电路、世界上第一个8位微处理器、世界上第一个1Gb的DRAM、世界上第一个GHz微处理器、世界上第一个多核处理器等众多集成电路历史上里程碑式的发明都在该会议上首次披露。自1954年以来,该会议已经成功举办68届。本次存内计算论文入选意味着此项核心技术已达到国际领先水平,得到了学术界的顶会认可,代表了芯片领域新的前进方向,在AI技术应用程度不断提升的今天,存内计算拥有巨大的发展前景。

您填的信息已提交,老师会在24小时之内与您联系

如果还有其他疑问请拨打以下电话

中国人民大学

中国人民大学 中国政法大学

中国政法大学 清华大学

清华大学 对外经济贸易大学

对外经济贸易大学 中央财经大学

中央财经大学